### Efficient Techniques for Scheduling DAG Applications in Distributed Environments

Thesis submitted to the Indian Institute of Technology Guwahati for the award of the degree

of

Doctor of Philosophy in Computer Science and Engineering

> Submitted by Debabrata Senapati

Under the guidance of **Dr. Arnab Sarkar and Dr. Chandan Karfa**

Department of Computer Science and Engineering Indian Institute of Technology Guwahati July, 2023

### Abstract

A Cyber-Physical System (CPS) integrates two sub-systems, a cyber sub-system and a physical sub-system. The cyber sub-system is often a heterogeneous distributed computing system that executes applications for regulating mechanisms associated with the physical sub-system, typically consisting of electro-mechanical components. Real-Time Cyber-Physical Systems (RT-CPSs) are characterized by their ability to respond to events that may happen in their operating environment within stipulated time bounds. The accuracy of these systems depends not only on the delivered results but also on their completion times. Applications in today's RT-CPSs are often represented by Directed Acyclic Graphs (DAGs) due to their distributed nature and complex interactions among component functionalities. In such DAGs, nodes represent tasks associated with the application, while edges denote inter dependencies among tasks. To meet functionality specific high-performance demands, these DAGs are often implemented on heterogeneous RT-CPS platforms where, (i) the same task may exhibit different execution time requirements on different processors, and (ii) inter-task messages containing the same amount of data may incur distinct transmission times on the different communication channels, due to variations in channel bandwidths. The RT-CPS applications may be aperiodically triggered by an external event or may execute in infinite loops, periodically acquiring data from the environment through sensors at a particular frequency, processing the same, and then producing processed data via actuators.

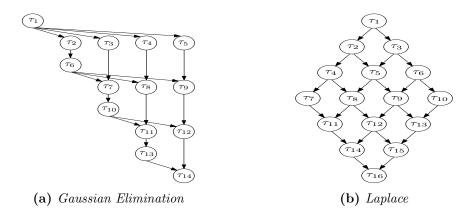

This dissertation deals with the design of resource allocation mechanisms for DAGstructured applications on heterogeneous distributed RT-CPSs. The thesis which unfolds through the dissertation is as follows: For the mentioned system scenarios, list-based design philosophy is effective towards obtaining low-overhead but efficient scheduling mechanisms for satisfying diverse objectives/constraints related to resource usage efficiency, timeliness, energy, security, temperature, etc. All list scheduling heuristics typically consist of two phases, (i) Task Prioritization: for listing tasks in a specific priority order, and (ii) Taskto-processor mapping: for allocating the tasks in the order of their priorities on suitable processors and associating with them appropriate execution start times. The contributions of this thesis are categorized into five phases as follows: (i) The first phase focuses on the development of an efficient real-time DAG-scheduling framework which attempts to minimize a generic penalty function. The designed penalty function can be amicably adopted towards its deployment in various application domains such as real-time cyber-physical systems like automotive and avionic systems, cloud computing, smart grids, etc. (ii) In the second phase, we develop a state-space search guided heuristic scheduling algorithm called HMDS, whose objective is to minimize *schedule length*. By controlling the nature and extent of state-space exploration, HMDS can adapt itself to deliver the best possible solution within a given time bound. (iii) A mechanism for co-scheduling multiple independent periodic DAG applications has been devised in the third phase. The objective of the scheduling algorithm is to minimize dissipated energy. (iv) Subsequently, in the fourth phase, a security-aware real-time DAG scheduling strategy has been designed. The scheme maximizes total security utility for a given application having known minimum security strength specifications for its messages. (v) Finally, in the last phase of the dissertation, we have developed a mechanism to construct minimum makespan schedules for precedence-constrained task graph applications with known thermal characteristics on a heterogeneous processing platform. The efficacy of the developed scheduling schemes has been extensively evaluated through simulation-based experiments using real-world benchmark task graphs. Prototype real-platform implementations as well as real-world case studies have also been presented to exhibit the practical applicability of the proposed algorithms.

**Keywords:** Cyber-physical systems (CPS), directed acyclic graph (DAG), real-time systems, distributed systems, heterogeneous platforms, list scheduling, makespan minimization, energy optimization, security-aware, temperature-aware

## Declaration

I certify that:

- a. The work contained in this thesis is original and has been done by me under the guidance of my supervisors.

- b. The work has not been submitted to any other Institute for any degree or diploma.

- c. I have followed the guidelines provided by the Institute in preparing the thesis.

- d. I have conformed to the norms and guidelines given in the Ethical Code of Conduct of the Institute.

- e. Whenever I have used materials (data, theoretical analysis, figures, and text) from other sources, I have given due credit to them by citing them in the text of the thesis and giving their details in the references.

Debabrata Senapati

#### Copyright

Attention is drawn to the fact that copyright of this thesis rests with its author. This copy of the thesis has been supplied on the condition that anyone who consults it is understood to recognize that its copyright rests with its author and that no quotation from the thesis and no information derived from it may be published without the prior written consent of the author.

This thesis may be made available for consultation within the Indian Institute of Technology Library and may be photocopied or lent to other libraries for the purposes of consultation.

## Certificate

This is to certify that this thesis entitled, "Efficient Techniques for Scheduling DAG Applications in Distributed Environments", being submitted by Debabrata Senapati, to the Department of Computer Science and Engineering, Indian Institute of Technology Guwahati, for partial fulfillment of the award of the degree of Doctor of Philosophy, is a bonafide work carried out by him under our supervision and guidance. The thesis, in our opinion, is worthy of consideration for award of the degree of Doctor of Philosophy in accordance with the regulation of the institute. To the best of our knowledge, it has not been submitted elsewhere for the award of the degree.

Dr. Arnab Sarkar Associate Professor Advanced Technology Development Centre IIT Kharagpur

Dr. Chandan Karfa Associate Professor Department of Computer Science and Engineering IIT Guwahati

## Dedicated to

रमं त्रथ्म म द्वी

nology

### my teachers, parents, wife and daughter

whose knowledge, blessing, love and inspiration paved my path of success ho. Distinguite of

#### Acknowledgements

My Ph.D. has been a long journey, full of exciting events and at times difficult and exhausting. This thesis would not be completed without the support and goodwill of several people. The following is an attempt at acknowledging them. I wish to express my deepest gratitude to my supervisors, Dr. Arnab Sarkar and Dr. Chandan Karfa, for their valuable guidance, inspiration, and advice. I feel very privileged to have had the opportunity to learn from and work with them. Their constant guidance and support paved the way for my development as a research scientist and changed my personality, ability, and nature in many ways. As a researcher, I am continually amazed at their clarity of thought and ability to get a fundamental idea behind a given problem with just a few questions. I benefited immensely from their unique advising style, which combines the correct balance between allowing students to perform independent research versus guiding them to ensure they pick the right topics of interest. It has been an honor to work with them.

Besides my supervisors, I would like to thank other members of my doctoral committee, Prof. Purandar Bhaduri, Prof. Hemangee K. Kapoor, and Dr. John Jose, for their insightful comments and encouragement. Their comments and suggestions helped me to widen my research from various perspectives. I want to express my heartful gratitude to the director, the deans, and other management of IIT Guwahati, whose collective efforts have made this institute a place for world-class studies and education. I am thankful to all faculty and staff of the Department of Computer Science and Engineering for extending their cooperation in terms of technical and official support to complete my research work successfully. I am thankful to the anonymous reviewers of my papers for their thoughtful suggestions and feedback.

I would also like to use this opportunity to thank all my colleagues in the Research Scholars' lab. for making the group such a cohesive unit and the lab. such a cozy place to be in through all these years. Thanks to my friends Swagat, Shakeel, Siva, Gyanendro, Prasen, Aswathy, Sumita and Priyanka for supporting and motivating me to overcome any problems at work or otherwise. The countless discussions and sharing of ideas have improved our research. I am also grateful to all my seniors and juniors, especially Piyoosh, Basina, Hema, Ujjwal, Subrata, Rakesh, Ramanuj, Moustafa, Pradeep, Arijit, Pawan, Dipojjal, Sisir, Chinmaya, Abhijit, Swarup, Anasua, Palas, Surajit, Alakesh, Manju, Nilotpal, Maithilee and many others, for their innumerable technical and non-technical supports. They all made my life at IIT Guwahati a memorable experience. Thanks to Rajesh, Sanjit, Kousik, and Puja for collaborating with me in research during my Ph.D. tenure. I am thankful to my dearest friend Jayanta, whose belief in me, continuous support, and encouragement gave me strength and confidence throughout this journey.

Most importantly, none of this would have been possible without the love and patience of my family. I am grateful to my parents for their unconditional love and consistent support in every event of my life. I am also very fortunate to have wonderful in-laws who gave me confidence and support at every step of my Ph.D. journey. I am forever indebted to my wife, Sasmita Rout. Without her love, sacrifice, constant encouragement and faith in me, none of this would have been possible. She has been incredibly supportive to me through the ups and downs over the past few years. I cannot thank her enough for being such an excellent life partner and friend. Finally, my wholehearted thanks to my daughter Miss Purvi Senapati, who is the ultimate inspiration source.

Before concluding, once again thanks to you all.

Debabrata Senapati

## Contents

| 1        | Intr | oducti | ion                                                                | 1  |

|----------|------|--------|--------------------------------------------------------------------|----|

|          | 1.1  | Backg  | round                                                              | 1  |

|          | 1.2  | Motiv  | ation and Objectives                                               | 3  |

|          |      | 1.2.1  | Makespan Minimization-based Scheduling Strategies                  | 5  |

|          |      | 1.2.2  | Energy-aware Real-time Scheduling Strategies                       | 6  |

|          |      | 1.2.3  | Scheduling Multiple Independent DAG Applications                   | 7  |

|          |      | 1.2.4  | Security-aware Real-time Scheduling                                | 7  |

|          |      | 1.2.5  | Temperature-aware Scheduling Strategies                            | 8  |

|          | 1.3  | Summ   | ary of Contributions                                               | 9  |

|          |      | 1.3.1  | PRESTO: A Penalty-aware Real-Time DAG Scheduler for Heteroge-      |    |

|          |      |        | neous Distributed Systems                                          | 9  |

|          |      | 1.3.2  | HMDS: A Makespan Minimizing DAG Scheduler for Heterogeneous        |    |

|          |      |        | Distributed Systems                                                | 10 |

|          |      | 1.3.3  | DPMRS: Energy-aware Real-time Scheduling of Multiple Periodic DAGs |    |

|          |      |        | on Heterogeneous Distributed Systems                               | 11 |

|          |      | 1.3.4  | SHIELD: Security-aware Scheduling for Real-time DAGs on Hetero-    |    |

|          |      |        | geneous Systems                                                    | 12 |

|          |      | 1.3.5  | TMDS: A Temperature-aware Makespan Minimizing DAG Scheduler        |    |

|          |      |        | for Heterogeneous Distributed Systems                              | 13 |

|          | 1.4  | Organ  | ization of the Thesis                                              | 15 |

| <b>2</b> | Bac  | kgrou  | nd on Real-time Systems and Literature Survey                      | 17 |

|          | 2.1  | Introd | uction                                                             | 17 |

#### CONTENTS

|   | 2.2                              | Real-t                                                                                                     | ime Systems                                                               | 17                                                                                                                                                         |

|---|----------------------------------|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                                  | 2.2.1                                                                                                      | Application Layer                                                         | 18                                                                                                                                                         |

|   |                                  |                                                                                                            | 2.2.1.1 Real-time Application Model                                       | 19                                                                                                                                                         |

|   |                                  | 2.2.2                                                                                                      | Real-time Scheduler                                                       | 20                                                                                                                                                         |

|   |                                  | 2.2.3                                                                                                      | Hardware Platform                                                         | 21                                                                                                                                                         |

|   | 2.3                              | Types                                                                                                      | of Real-time Application Constraints                                      | 24                                                                                                                                                         |

|   | 2.4                              | A Cla                                                                                                      | ssification of Real-Time Scheduling Policies                              | 26                                                                                                                                                         |

|   | 2.5                              | Survey                                                                                                     | v of Scheduling Algorithms                                                | 27                                                                                                                                                         |

|   |                                  | 2.5.1                                                                                                      | Makespan Minimization Scheduling Strategies                               | 28                                                                                                                                                         |

|   |                                  | 2.5.2                                                                                                      | Monetary Cost Minimization Real-time Scheduling Policies                  | 29                                                                                                                                                         |

|   |                                  | 2.5.3                                                                                                      | Energy-aware Real-time Scheduling Strategies                              | 30                                                                                                                                                         |

|   |                                  | 2.5.4                                                                                                      | Scheduling Multiple Independent DAG Applications                          | 31                                                                                                                                                         |

|   |                                  | 2.5.5                                                                                                      | Security-aware Real-time Scheduling Strategies                            | 32                                                                                                                                                         |

|   |                                  | 2.5.6                                                                                                      | Temperature-aware Scheduling Strategies                                   | 33                                                                                                                                                         |

|   | 2.6                              | Summ                                                                                                       | ary                                                                       | 34                                                                                                                                                         |

|   |                                  |                                                                                                            |                                                                           |                                                                                                                                                            |

| 3 | $\mathbf{PR}$                    | ESTO:                                                                                                      | A Penalty-aware Real-time Scheduler for Task Graphs on Het-               |                                                                                                                                                            |

| 3 |                                  |                                                                                                            | A Penalty-aware Real-time Scheduler for Task Graphs on Het-<br>s Platform | 35                                                                                                                                                         |

| 3 |                                  | geneou                                                                                                     |                                                                           |                                                                                                                                                            |

| 3 | erog                             | <b>geneou</b><br>Introd                                                                                    | s Platform                                                                | 35                                                                                                                                                         |

| 3 | <b>ero</b> g<br>3.1              | <b>geneou</b><br>Introd<br>Syster                                                                          | s Platform                                                                | <b>35</b><br>35                                                                                                                                            |

| 3 | <b>erog</b><br>3.1<br>3.2        | geneou<br>Introd<br>Syster<br>Const                                                                        | s Platform<br>uction                                                      | <b>35</b><br>35<br>37                                                                                                                                      |

| 3 | erog<br>3.1<br>3.2<br>3.3        | geneou<br>Introd<br>Syster<br>Const                                                                        | s Platform uction                                                         | <b>35</b><br>35<br>37<br>39                                                                                                                                |

| 3 | erog<br>3.1<br>3.2<br>3.3        | geneou<br>Introd<br>Syster<br>Const<br>PRES                                                                | s Platform uction                                                         | <ul> <li>35</li> <li>35</li> <li>37</li> <li>39</li> <li>41</li> </ul>                                                                                     |

| 3 | erog<br>3.1<br>3.2<br>3.3        | geneou<br>Introd<br>Syster<br>Const<br>PRES<br>3.4.1                                                       | s Platform uction                                                         | <ul> <li>35</li> <li>37</li> <li>39</li> <li>41</li> <li>41</li> </ul>                                                                                     |

| 3 | erog<br>3.1<br>3.2<br>3.3        | geneou<br>Introd<br>Syster<br>Const<br>PRES<br>3.4.1<br>3.4.2                                              | s Platform uction                                                         | <ul> <li>35</li> <li>37</li> <li>39</li> <li>41</li> <li>41</li> <li>44</li> </ul>                                                                         |

| 3 | erog<br>3.1<br>3.2<br>3.3        | geneou<br>Introd<br>Syster<br>Const<br>PRES<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4                            | s Platform uction                                                         | <ul> <li>35</li> <li>37</li> <li>39</li> <li>41</li> <li>41</li> <li>44</li> <li>46</li> </ul>                                                             |

| 3 | erog<br>3.1<br>3.2<br>3.3<br>3.4 | geneou<br>Introd<br>Syster<br>Const<br>PRES<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4                            | s Platform uction                                                         | <ul> <li>35</li> <li>37</li> <li>39</li> <li>41</li> <li>41</li> <li>44</li> <li>46</li> <li>49</li> </ul>                                                 |

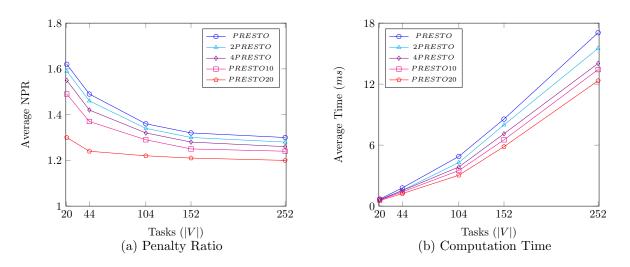

| 3 | erog<br>3.1<br>3.2<br>3.3<br>3.4 | geneou<br>Introd<br>Syster<br>Const<br>PRES<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>Exper                   | s Platform uction                                                         | <ul> <li>35</li> <li>35</li> <li>37</li> <li>39</li> <li>41</li> <li>41</li> <li>44</li> <li>46</li> <li>49</li> <li>50</li> </ul>                         |

| 3 | erog<br>3.1<br>3.2<br>3.3<br>3.4 | geneou<br>Introd<br>Syster<br>Const<br>PRES<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>Exper<br>3.5.1          | s Platform uction                                                         | <ul> <li>35</li> <li>35</li> <li>37</li> <li>39</li> <li>41</li> <li>41</li> <li>44</li> <li>46</li> <li>49</li> <li>50</li> <li>51</li> </ul>             |

| 3 | erog<br>3.1<br>3.2<br>3.3<br>3.4 | geneou<br>Introd<br>Syster<br>Const<br>PRES<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>Exper<br>3.5.1<br>3.5.2 | s Platform uction                                                         | <ul> <li>35</li> <li>35</li> <li>37</li> <li>39</li> <li>41</li> <li>41</li> <li>44</li> <li>46</li> <li>49</li> <li>50</li> <li>51</li> <li>54</li> </ul> |

| 3 | erog<br>3.1<br>3.2<br>3.3<br>3.4 | geneou<br>Introd<br>Syster<br>Const<br>PRES<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>Exper<br>3.5.1<br>3.5.2 | s Platform<br>uction                                                      | <b>35</b><br>35<br>37<br>39<br>41<br>41<br>44<br>46<br>49<br>50<br>51<br>54<br>55                                                                          |

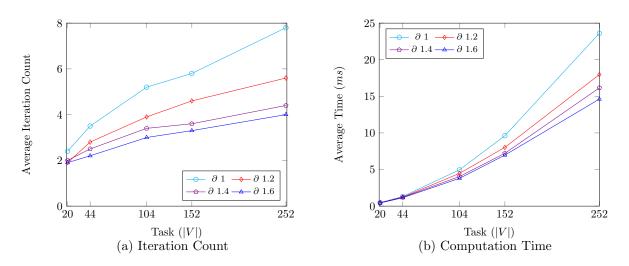

|   |                        |        | 3.5.3.4   | Experiment-4: Iteration counts and run-times                         | 59 |

|---|------------------------|--------|-----------|----------------------------------------------------------------------|----|

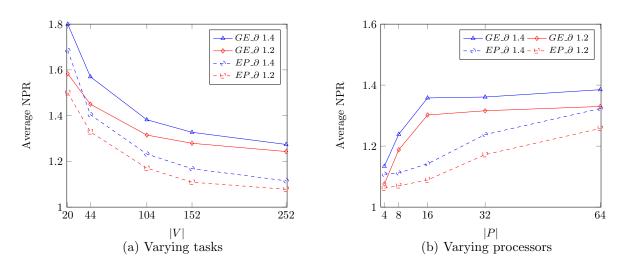

|   |                        |        | 3.5.3.5   | Experiment-5: Normalized penalty ratios w.r.t. tasks, pro-           |    |

|   |                        |        |           | cessors, CCR and heterogeneity                                       | 59 |

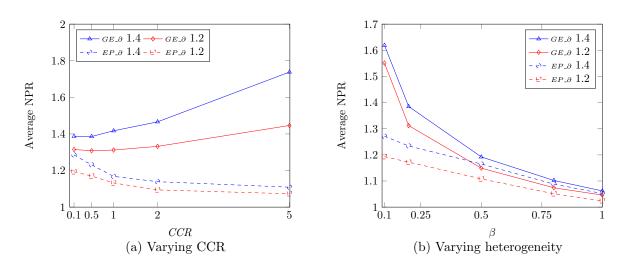

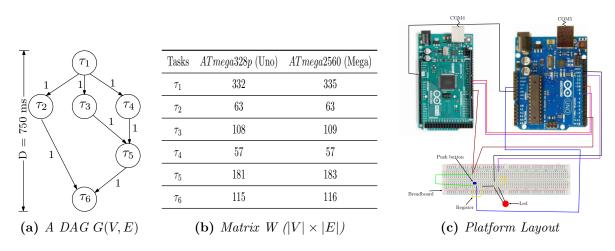

|   | 3.6                    | A Pro  | totype In | plementation                                                         | 61 |

|   | 3.7                    | Case S | Studies . |                                                                      | 65 |

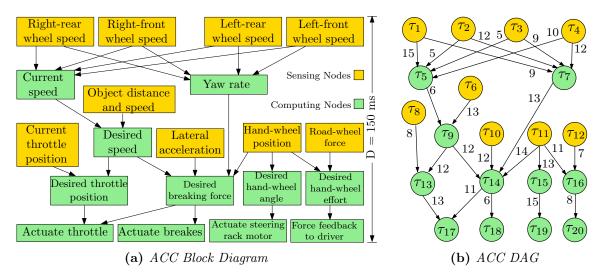

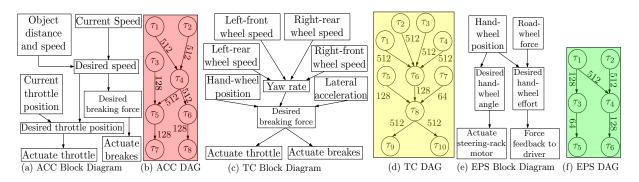

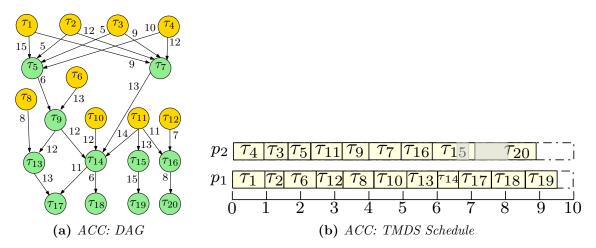

|   |                        | 3.7.1  | Adaptiv   | e Cruise Controller in Automotive Systems                            | 66 |

|   |                        | 3.7.2  | Intellige | nt Surveillance in a Fog Environment                                 | 67 |

|   | 3.8                    | Summ   | ary       |                                                                      | 69 |

| 4 | $\mathbf{H}\mathbf{M}$ | DS: A  | Makesp    | oan Minimizing DAG Scheduler for Heterogeneous Dis-                  |    |

|   | $\operatorname{trib}$  | uted S | ystems    |                                                                      | 71 |

|   | 4.1                    | Introd | uction .  |                                                                      | 71 |

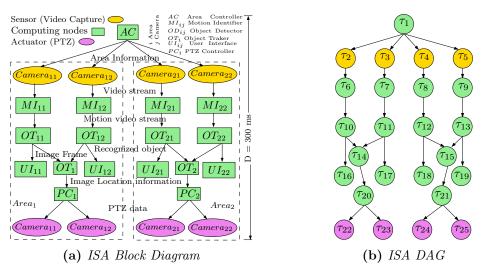

|   | 4.2                    | System | n Model   |                                                                      | 73 |

|   | 4.3                    | The P  | roposed S | Schedulers                                                           | 74 |

|   |                        | 4.3.1  | HMDS-I    | Bl: The Baseline List Scheduler                                      | 74 |

|   |                        | 4.3.2  | HMDS:     | DFBB Search Based Extension to HMDS-Bl                               | 78 |

|   |                        |        | 4.3.2.1   | Pruning Mechanism 1: Using a lower bound heuristic function          | 83 |

|   |                        |        | 4.3.2.2   | Pruning Mechanism 2: Cap on maximum $\# {\rm processor}$ choices     | 84 |

|   |                        |        | 4.3.2.3   | Pruning Mechanism 3: $O_{EFT}$ based cap on $\#$ procssor choices    | 85 |

|   |                        |        | 4.3.2.4   | Pruning Mechanism 4: Cap on solution generation times $\ . \ .$      | 86 |

|   |                        |        | 4.3.2.5   | Complexity Analysis                                                  | 86 |

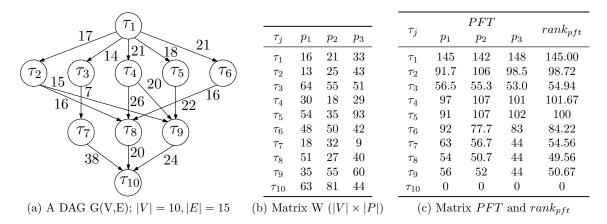

|   | 4.4                    | Exper  | iments an | d Results                                                            | 87 |

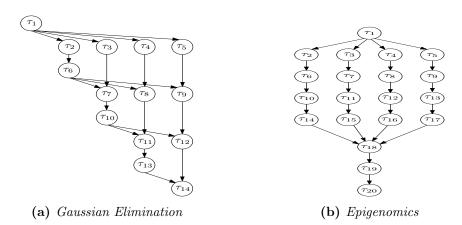

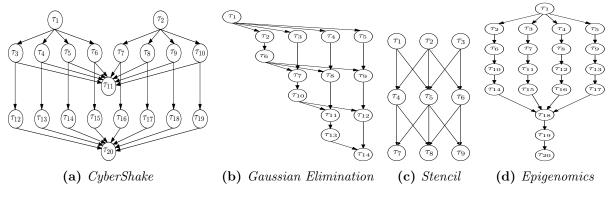

|   |                        | 4.4.1  | Experim   | nental Setup                                                         | 87 |

|   |                        | 4.4.2  | Perform   | ance Metrics                                                         | 89 |

|   |                        | 4.4.3  | Perform   | ance Results                                                         | 89 |

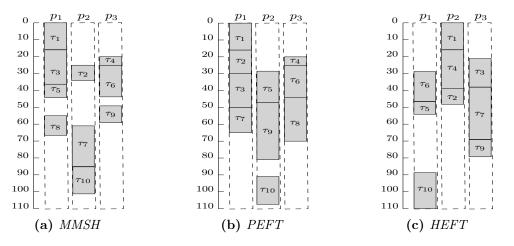

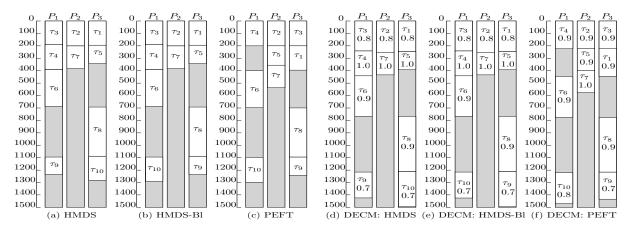

|   |                        |        | 4.4.3.1   | Experiment-1: Pair-wise <i>makespan</i> comparison of algorithms     | 90 |

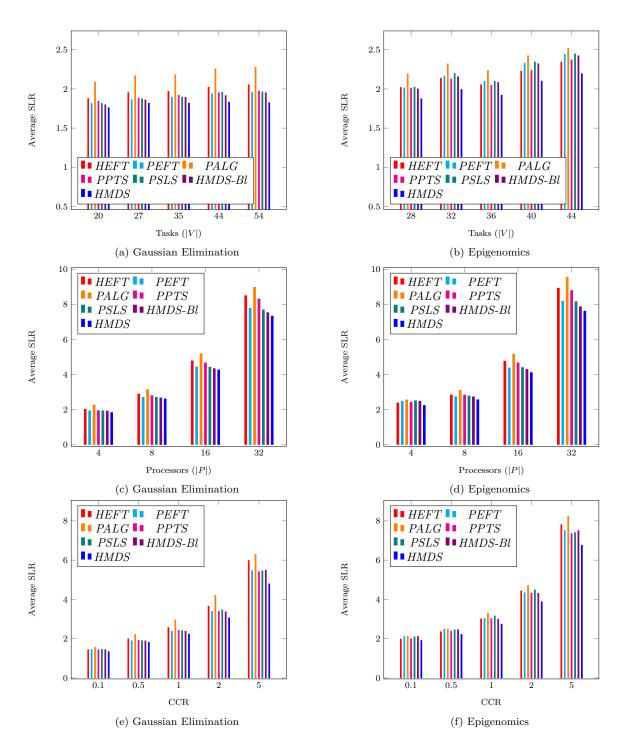

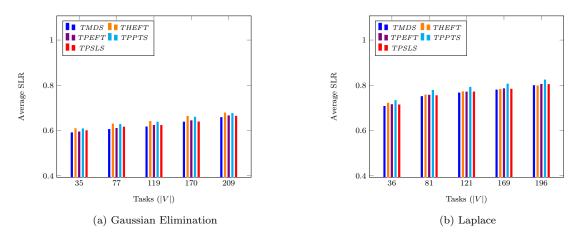

|   |                        |        | 4.4.3.2   | Experiment-2: Comparison of schedule length ratios                   | 90 |

|   |                        |        | 4.4.3.3   | Experiment-3: Comparison of run-times                                | 93 |

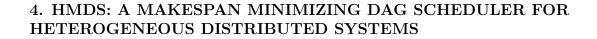

|   |                        |        | 4.4.3.4   | Experiment-4: Bound on $\#$ processor choices                        | 93 |

|   |                        |        | 4.4.3.5   | Experiment-5: Effect of $O_{EFT}$ based bound $\ldots \ldots \ldots$ | 95 |

|   |                        |        | 4.4.3.6   | Experiment-6: Effect of hard run time caps                           | 95 |

|   |                        |        | 4.4.3.7   | Experiment-7: HMDS vs. HMDS-Bl                                       | 96 |

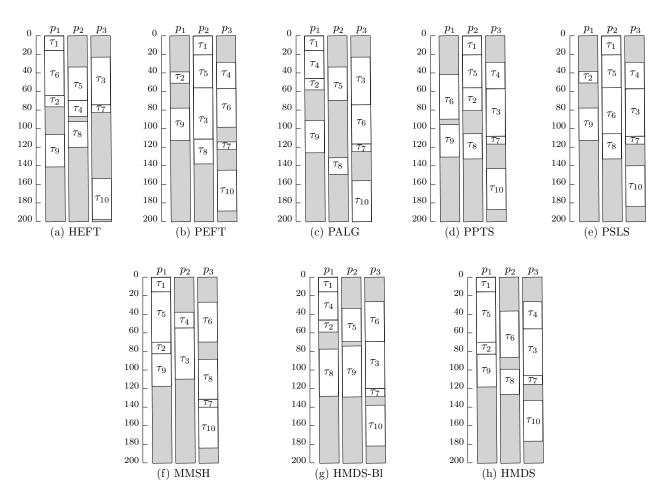

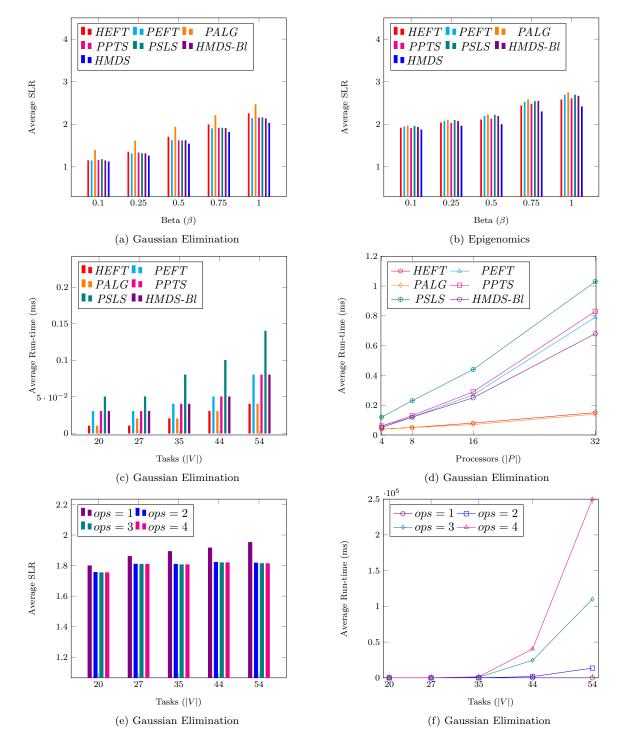

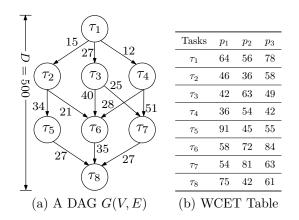

|   | 4.5                    | Case S | Study: Tr | action Control System                                                | 97 |

#### CONTENTS

|          | 4.6 | Summ   | ary                                                                                                | 100            |

|----------|-----|--------|----------------------------------------------------------------------------------------------------|----------------|

| <b>5</b> | DP  | MRS:   | An Energy-aware Real-time Scheduling of Multiple Periodi                                           | C              |

|          | DA  |        | Heterogeneous Systems                                                                              | 101            |

|          | 5.1 | Introd | luction                                                                                            | 101            |

|          | 5.2 | System | n Models                                                                                           | 102            |

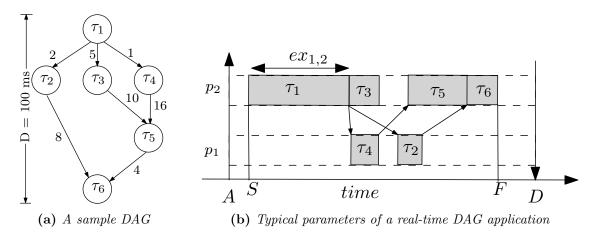

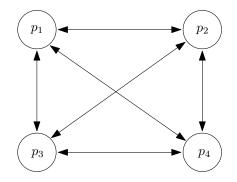

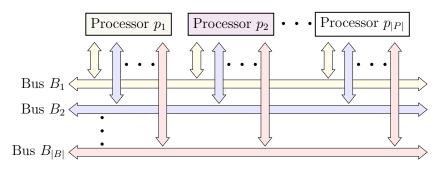

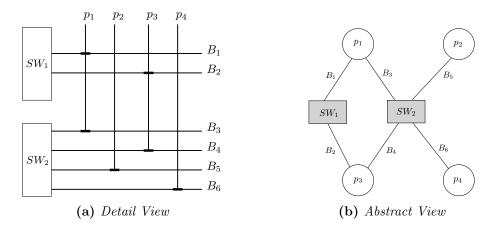

|          |     | 5.2.1  | Application and Platform Model                                                                     | 102            |

|          |     | 5.2.2  | Power and Energy Model                                                                             | 104            |

|          | 5.3 | The P  | Proposed Schedulers                                                                                | 106            |

|          |     | 5.3.1  | The DPMRS Algorithm                                                                                | 106            |

|          |     |        | 5.3.1.1 Function periodicMerge() $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                | 108            |

|          |     |        | 5.3.1.2 Function ERRRank() $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 109            |

|          |     |        | 5.3.1.3 Function $DPMRS()$                                                                         | 112            |

|          |     | 5.3.2  | Complexity Analysis                                                                                | 117            |

|          | 5.4 | Exper  | iments and Results                                                                                 | 118            |

|          |     | 5.4.1  | Experimental Setup                                                                                 | 118            |

|          |     | 5.4.2  | Performance Metrics                                                                                | 121            |

|          |     | 5.4.3  | Comparison with Related Works                                                                      | 122            |

|          |     | 5.4.4  | Performance Results                                                                                | 124            |

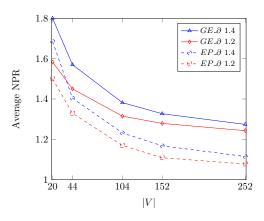

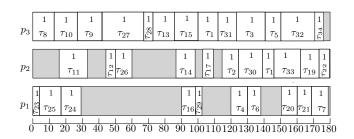

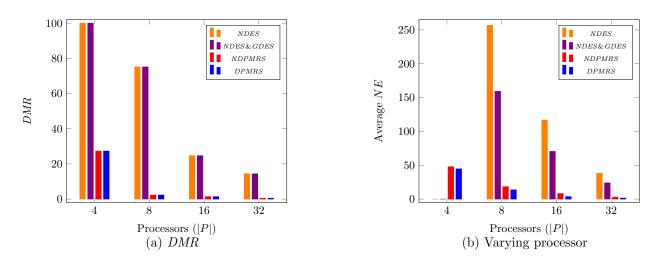

|          |     |        | 5.4.4.1 Experiment-1: Effect of variation in $\#$ processors                                       | 124            |

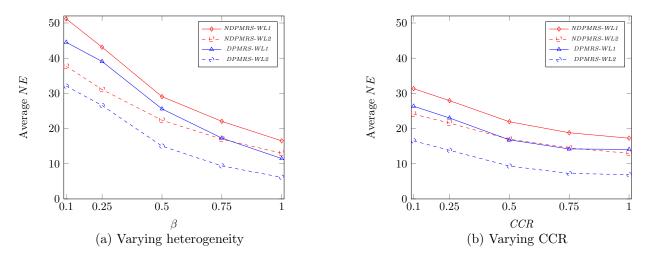

|          |     |        | 5.4.4.2 Experiment-2: Effect of variation in CCR and heterogeneity                                 | 126            |

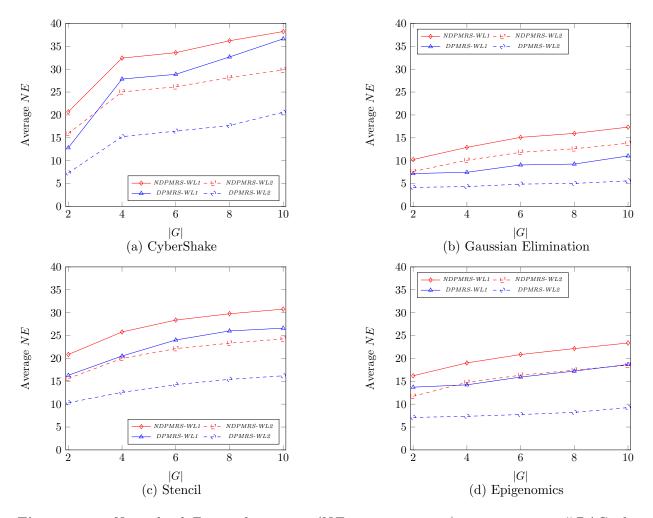

|          |     |        | 5.4.4.3 Experiment-3: Effect of variation in $\#$ tasks                                            | 127            |

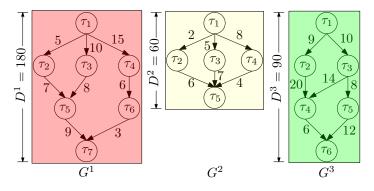

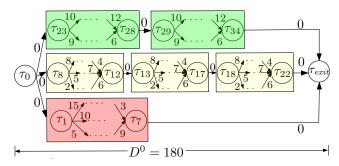

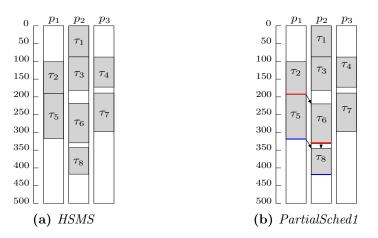

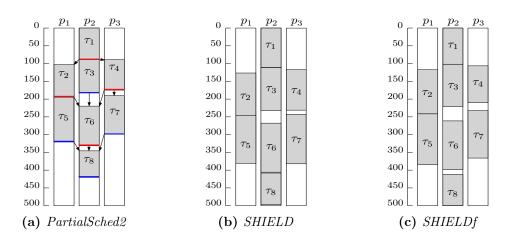

|          | 5.5 | Case S | Study: Automotive Control System                                                                   | 128            |

|          | 5.6 | Summ   | ary                                                                                                | 131            |

| 6        | SHI | ELD:   | Security-aware Scheduling for Real-time DAGs on Heteroge                                           | <del>)</del> - |

|          | neo | us Sys | tems                                                                                               | 133            |

|          | 6.1 | Introd | luction                                                                                            | 133            |

|          | 6.2 | System | n Models                                                                                           | 134            |

|          |     | 6.2.1  | Application and Platform Model                                                                     | 135            |

|          |     | 6.2.2  | Security Model                                                                                     |                |

|          | 6.3 | SHIEI  | LD: The Proposed Scheduler                                                                         |                |

|          |     | 6.3.1  | Task Prioritization                                                                                |                |

|   |                                               | 6.3.2                                                                                           | Processor Allocation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 39                                                                                                                                             |

|---|-----------------------------------------------|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                                               | 6.3.3                                                                                           | Security Enhancement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 41                                                                                                                                             |

|   |                                               |                                                                                                 | 6.3.3.1 SHIELDb: The Baseline List Scheduler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 42                                                                                                                                             |

|   |                                               |                                                                                                 | 6.3.3.2 SHIELD: An Enhancement over SHIELDb                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 45                                                                                                                                             |

|   |                                               | 6.3.4                                                                                           | Complexity Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 49                                                                                                                                             |

|   | 6.4                                           | Exper                                                                                           | iments and Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 51                                                                                                                                             |

|   |                                               | 6.4.1                                                                                           | Experimental Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 52                                                                                                                                             |

|   |                                               | 6.4.2                                                                                           | Performance Metrics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 54                                                                                                                                             |

|   |                                               | 6.4.3                                                                                           | Performance Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 54                                                                                                                                             |

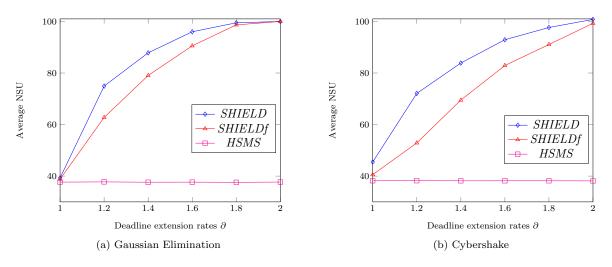

|   |                                               |                                                                                                 | 6.4.3.1 Experiment-1: Effect of variation in deadline extension rates 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 55                                                                                                                                             |

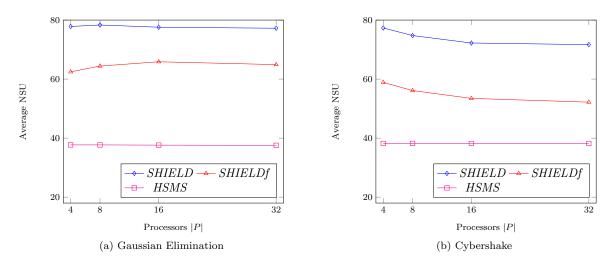

|   |                                               |                                                                                                 | 6.4.3.2 Experiment-2: Effect of variation in $\#$ processors 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 55                                                                                                                                             |

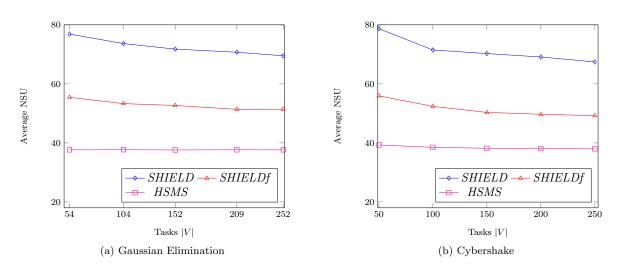

|   |                                               |                                                                                                 | 6.4.3.3 Experiment-3: Effect of variation in varying tasks 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 56                                                                                                                                             |

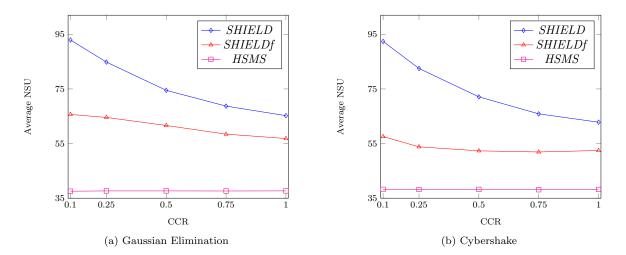

|   |                                               |                                                                                                 | 6.4.3.4 Experiment-4: Effect of variation in CCR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 58                                                                                                                                             |

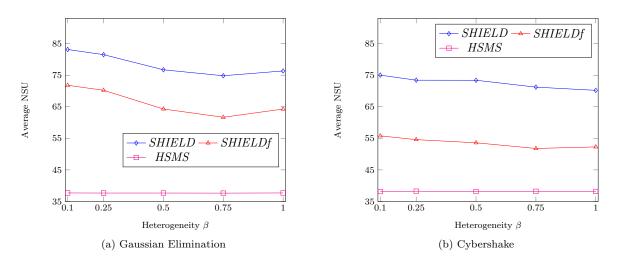

|   |                                               |                                                                                                 | 6.4.3.5 Experiment-5: Effect of variation in heterogeneity 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 58                                                                                                                                             |

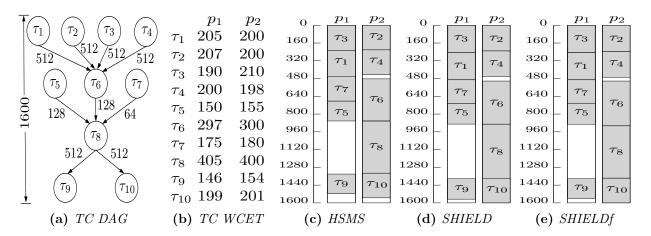

|   | 6.5                                           | Case S                                                                                          | Study: Traction Control System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 59                                                                                                                                             |

|   | 6.6                                           | Summ                                                                                            | ary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 60                                                                                                                                             |

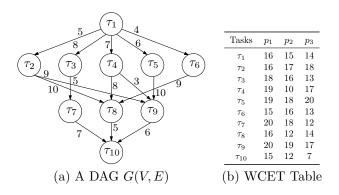

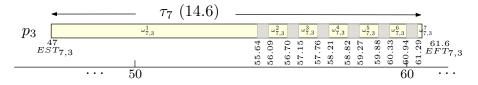

| 7 |                                               |                                                                                                 | The second |                                                                                                                                                |

| 1 |                                               |                                                                                                 | Temperature-aware Makespan Minimizing DAG Scheduler for<br>neous Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                |

|   | 7.1                                           | eruger                                                                                          | ieuus Systems 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 61                                                                                                                                             |

|   |                                               | Introd                                                                                          | uction 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <b>61</b>                                                                                                                                      |